Se trata de un equipo de de investigadores y estudiantes de grado y posgrado del Laboratorio de Comunicaciones Digitales (LCD), particularmente el grupo de investigación en micro-nanotecnología, que idearon íntegramente el chip, y fabricado en EE.UU. por la empresa MOSIS-IBM.

La cooperación se realiza en el marco de un convenio entre la FCEFyN y la empresa MOSIS, que permite la fabricación periódica de diseños de micro-nanoelectrónica desarrollados en esta casa de estudios. El proyecto, además, contó con el apoyo de la Fundación Tarpuy.

Características

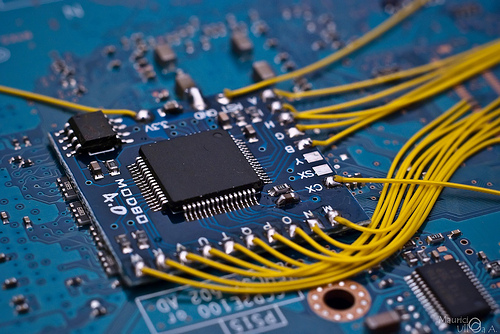

El circuito integrado desarrollado por el LCD comprende un conversor analógico digital (ADC) intercalado temporalmente (Time-Interleaved ADC) el cual se compone de 8 celdas de muestreo y retención (T/H) y 16 bloques de conversión de aproximación sucesiva (SAR-ADC) de 6 bits de resolución. Estos bloques de T/H y SAR-ADC fueron diseñados para operar en paralelo y alcanzar una tasa de conversión total de más de 2 Giga-Muestras por segundo, esto es más de 2000 millones de muestras analógicas digitalizadas por segundo, lo cuál es más de la velocidad necesaria para la mayoría de las comunicaciones en dispositivos móviles y redes de datos.

Además, el diseño contempla múltiples circuitos de calibración (offset, fase y ganancia) e interfaces de alta velocidad para la comunicación con otros chips y la tecnología de fabricación utilizada fue de 130 nanómetros tipo CMOS.

Los conversores A/D, como el desarrollado en el LCD, componen la interfaz imprescindible entre el mundo real (analógico) y el mundo virtual (digital) y que ha permitido (junto al avance de otras tecnologías) el crecimiento abrumadador de las comunicaciones por fibra-óptica e inalámbricas de los últimos años.

Actualmente, el chip está siendo evaluado y probado para recabar datos de desempeño y planean ser reportados en publicaciones nacionales e internacionales del área de investigación.

Más información, acá.